XCVE2802-2MSEVSVH1760 At-A-Glance

XCVE2802-2MSEVSVH1760 At-A-Glance

This post is an XCVE2802-2MSEVSVH1760 at-a-glance. This part is featured on the AMD Versal™ AI Edge Series VEK280 Evaluation Kit (EK-VEK280-PP-G) https://www.xilinx.com/products/boards-and-kits/vek280.html and lists XCVE2802-2MSEVSVH1760 info and links to key information and documents.

Click [ https://www.centennialsoftwaresolutions.com/post/xcvc1902-1msevsva2197-decoded ] if you need a XCVC1902-1MSEVSVA2197 at-a-glance, This part is featured on the first Versal™ AI Core series evaluation kit (it actually uses a XCVC1902-2MSEVSVA2197)

It includes:

-

XCVE2802-2MSEVSVH1760 Ordering Information Decode

-

XCVE2802-2MSEVSVH1760 Resources

-

XCVE2802-2MSEVSVH1760 Maximum I/O

-

XCVE2802-2MSEVSVH1760 I/O Overview

-

XCVE2802-2MSEVSVH1760 Voltage

-

XCVE2802-2MSEVSVH1760 Vivado Part Number

-

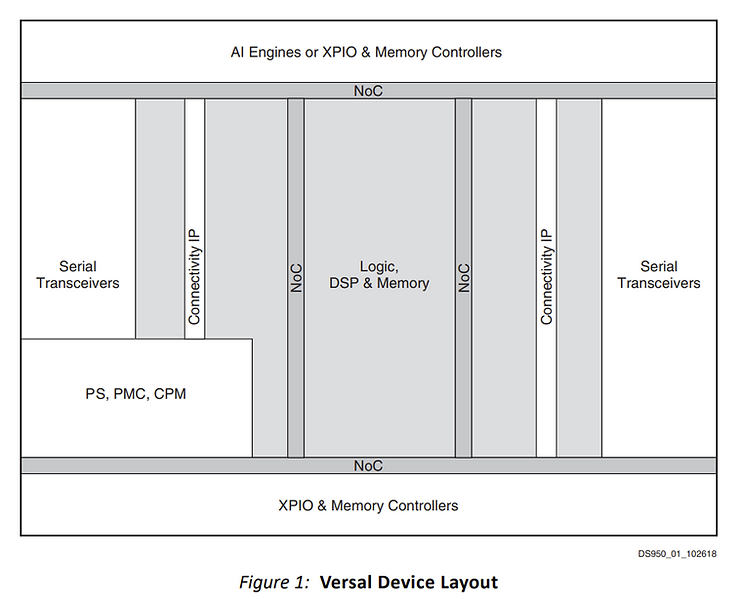

XCVE2802-2MSEVSVH1760 Physical Layout

-

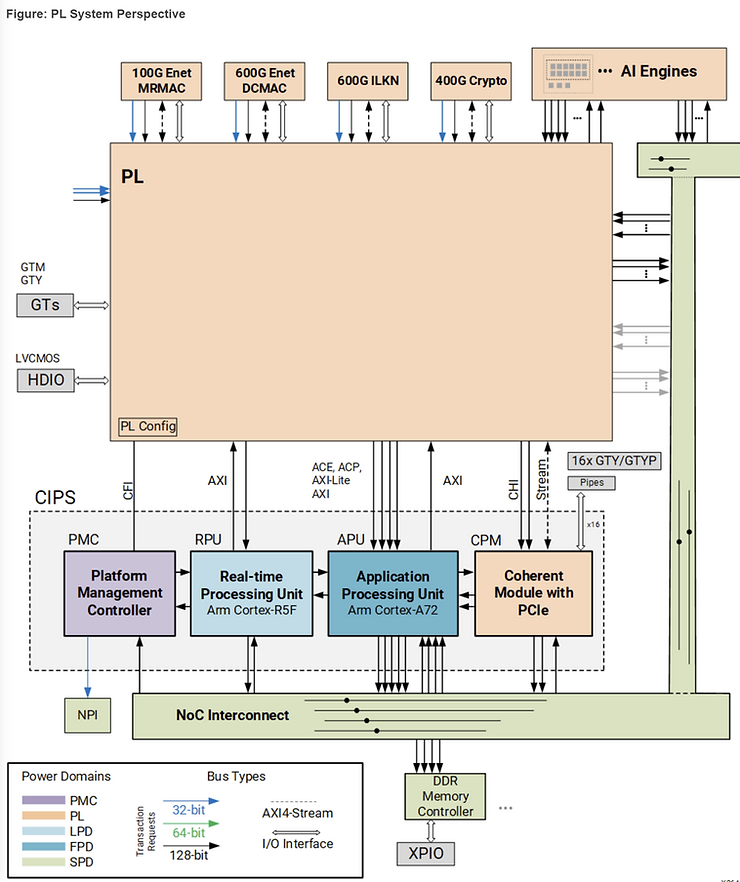

XCVE2802-2MSEVSVH1760 PL System Perspective

-

XCVE2802-2MSEVSVH1760 Boot

-

XCVE2802-2MSEVSVH1760 Software Development

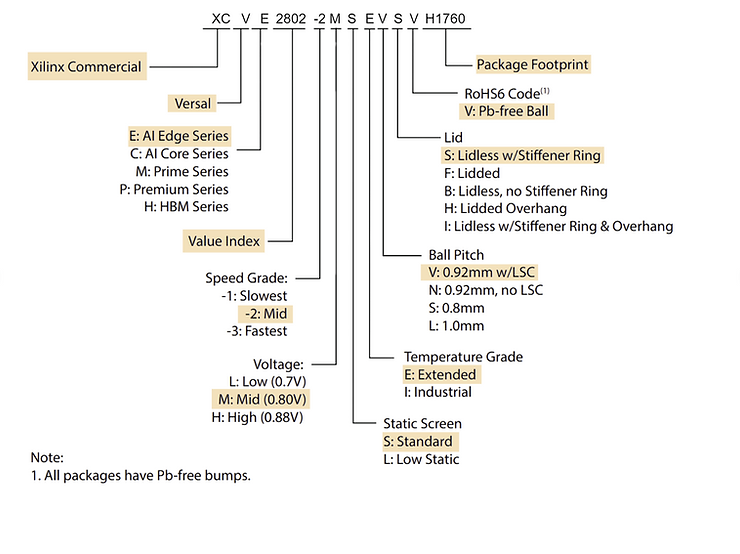

XCVE2802-2MSEVSVH1760 Ordering Information Decode

From Figure 3: Versal Device Ordering Information

https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page=35

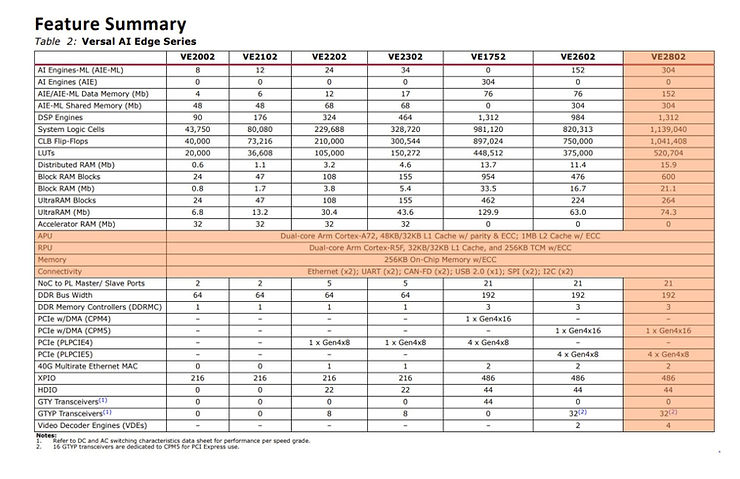

XCVE2802-2MSEVSVH1760 Resources

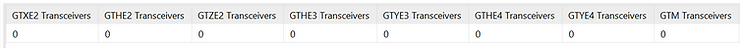

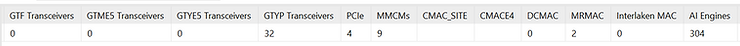

From Table 2: Versal AI Edge Series https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page=3

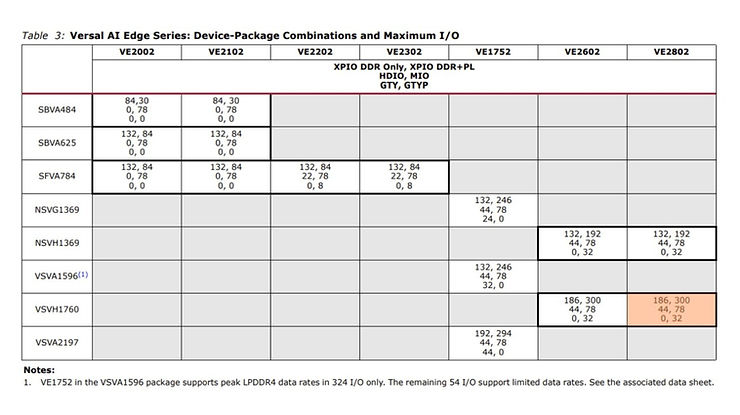

XCVE2802-2MSEVSVH1760 Maximum I/O

From Table 3: Versal AI Edge Series: Device-Package Combinations and Maximum I/O https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page=4

-

XPIO DDR: 186

-

XPIO DDR+PL: 300

-

HDIO (high-density I/O): 44

-

MIO (multiplex I/O): 78

-

GTY: 0

-

Versal ACAP GTY and GTYP Transceivers Architecture Manual (AM002) @ https://docs.xilinx.com/r/en-US/am002-versal-gty-transceivers

- GTY Description @ https://docs.xilinx.com/r/en-US/am002-versal-gty-transceivers/Features

-

26.5625 Max Gb/s, 1.2 Min Gb/s , https://www.xilinx.com/support/documents/data_sheets/ds957-versal-ai-core.pdf#page=58

-

-

GTYP: 32

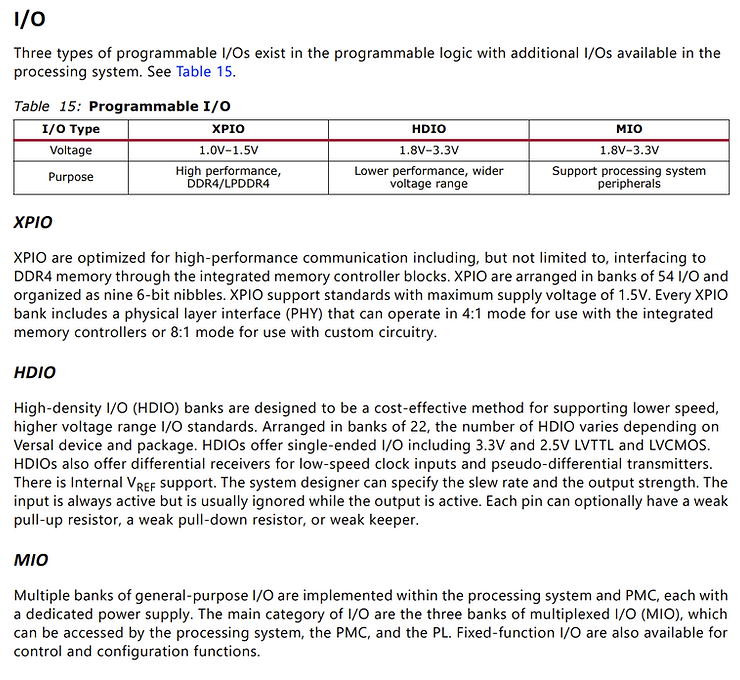

XCVE2802-2MSEVSVH1760 I/O Overview

From https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page%20=28

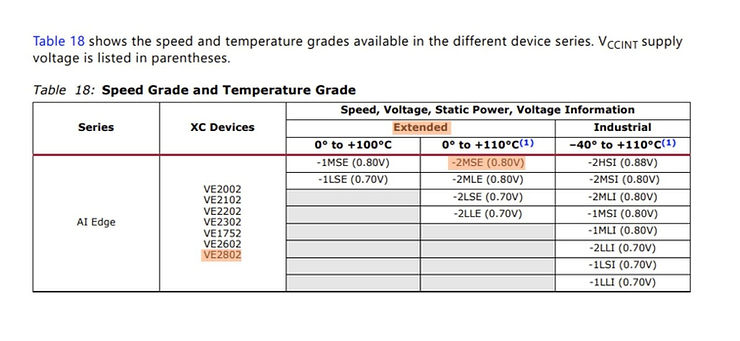

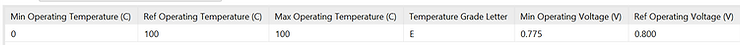

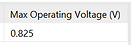

XCVE2802-2MSEVSVH1760 Voltage

From: https://www.xilinx.com/support/documents/data_sheets/ds957-versal-ai-core.pdf#page=7 (DS957)

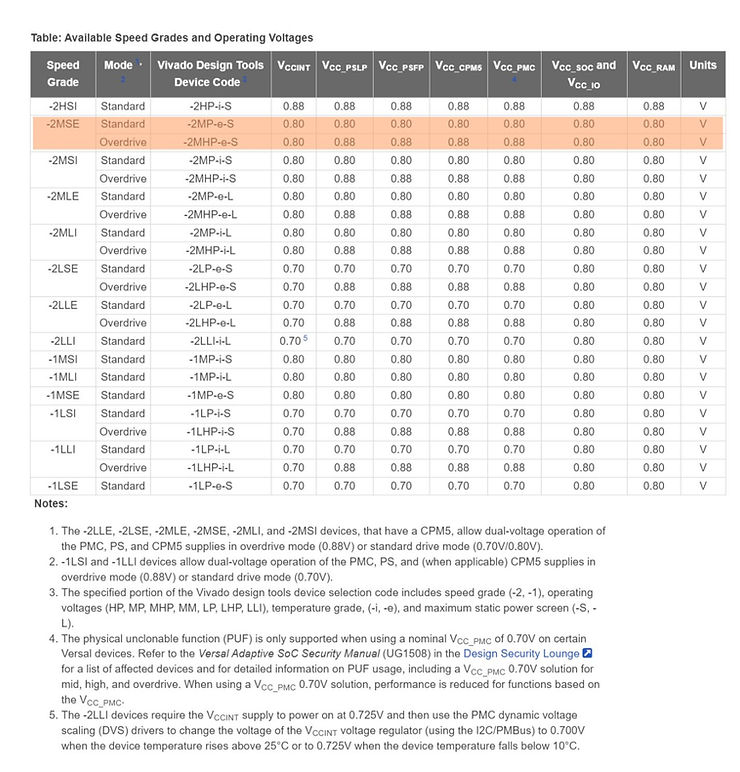

The specified portion of the Vivado design tools device selection code includes speed grade (-3, \-2, -1), operating voltages (HP, MP, MHP, MM, LP, LHP, LLI), temperature grade, (-i, \-e, -m), and maximum static power screen (\-S, -L).

From: https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page=33 (DS950)

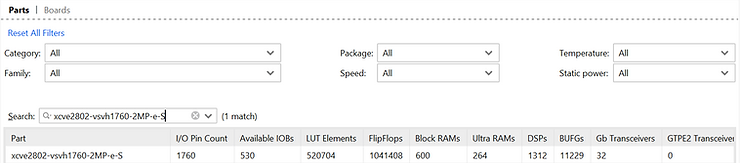

XCVE2802-2MSEVSVH1760 Vivado Part Number

From Table: Available Speed Grades and Operating Voltages https://docs.xilinx.com/r/en-US/ds958-versal-ai-edge/Available-Speed-Grades-and-Operating-Voltages

The XCVE2802-2MSEVSVH1760 Vivado Part # is xcve2802-vsvh1760-2MP-e-S (Vivado 2022.1)

=

XCVE2802-2MSEVSVH1760 Physical Layout

From https://docs.xilinx.com/v/u/en-US/ds950-versal-overview#page=12

From https://docs.xilinx.com/r/en-US/am011-versal-acap-trm/PL-Block-Diagram

XCVE2802-2MSEVSVH1760 PL System Perspective

XCVE2802-2MSEVSVH1760 Boot

https://docs.xilinx.com/r/en-US/am011-versal-acap-trm/Non-Secure-Boot-Flow

https://docs.xilinx.com/r/en-US/am011-versal-acap-trm/Secure-Boot-Flow

XCVE2802-2MSEVSVH1760 Software Development

https://docs.xilinx.com/r/en-US/ug1304-versal-acap-ssdg

References To Items Used In This Post

Logo from https://library.amd.com/media/ (requires a password)

Related Information

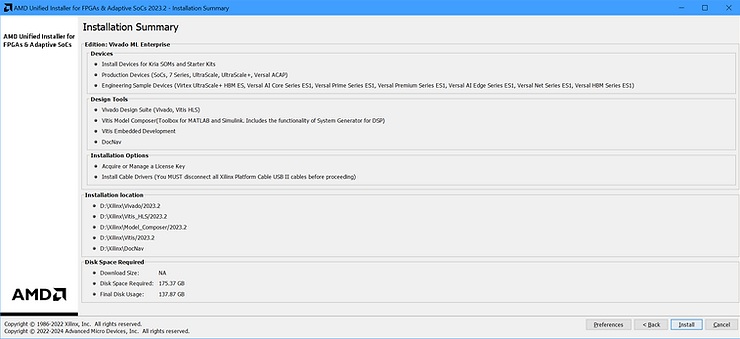

2023.2 Installation Summary

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools.html

AMD Unified Installer for FPGAs & Adaptive SoCs 2023.2 SFD (TAR/GZIP - 103.92 GB)

MD5 SUM Value : 64d64e9b937b6fd5e98b41811c74aab2